# GTI – ÜBUNG 9

CMOS, NAND, PAL, FLIPFLOPS

▶ Beschreibung:

Sei die Schaltfunktion  $f(x_3, x_2, x_1, x_0) = x_0 \overline{x_1} \overline{x_2} + x_0 \overline{x_1} \overline{x_3}$  gegeben.

► Begriffsklärung:

#### CMOS:

- Akronym für Complementary MOS

- Komposition aus komplementären NMOS-Transistor-Feld (Pull-Down) und PMOS-Transistorfeld (Pull-Up)

- Eine Schaltfunktion wird also zwei Mal umgesetzt

- Vorteil: keine Energieverbrauch im festen Schaltzustand, da Stromfluss nur während der Schaltvorgänge

#### **Transistor:**

- Transfer Resistor (steuerbarer Widerstand)

- Nutzung als steuerbarer Schalter (hier!) bzw. Verstärker

- o Elementares Element nahezu jeglicher Digitalschaltung

#### MOS:

- Spezieller Typ eines Transistors

- o Elemente:

Source: Quelle bzw. Eingang des Transistors

o Gate: positiv angelegte Spannung erzeugt Stromfluss zwischen Source und Drain

o Drain: Ziel bzw. Ausgang des Transistors

### **PMOS**

- Unterart des MOS-Transistor (bestimmte Dotierung: p-dotiert (Löcher))

- Genutzt im Pull-Up Netz eines CMOS

- Sperrt bei logischer 1 (d.h. 5 V) (deshalb Darstellung mit Inverter)

#### **NMOS**

- Unterart des MOS-Transistor (bestimmte Dotierung: n-dotiert)

- Genutzt im Pull-Down Netz eines CMOS

- Öffnet bei logischer 1 (d.h. 5 V)

### Aufgabe 1 – CMOS

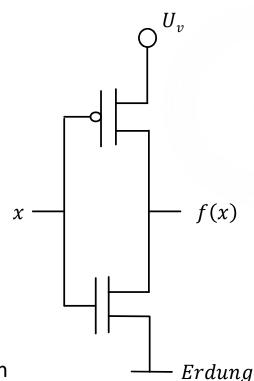

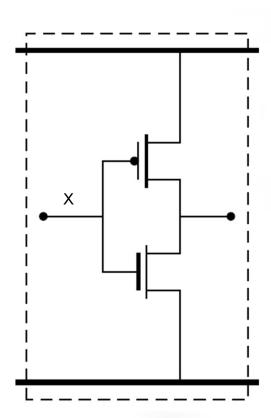

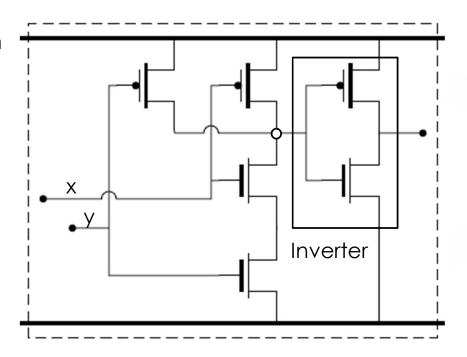

Beispiel: CMOS – Darstellung eines Inverters

$$\circ \quad f(x) = \bar{x}$$

### Pull-Up:

- Realisiert normale Schaltfunktion  $f(x) = \bar{x}$

- Besteht nur aus negativen Eingängen (PMOS)

#### Pull-Down:

- Realisiert negierte Schaltfunktion  $f(x) = \bar{x} = x$

- Besteht nur aus positiven Eingängen (NMOS)

- o Falls negatives Literal im Ausdruck; Inverter vorschalten

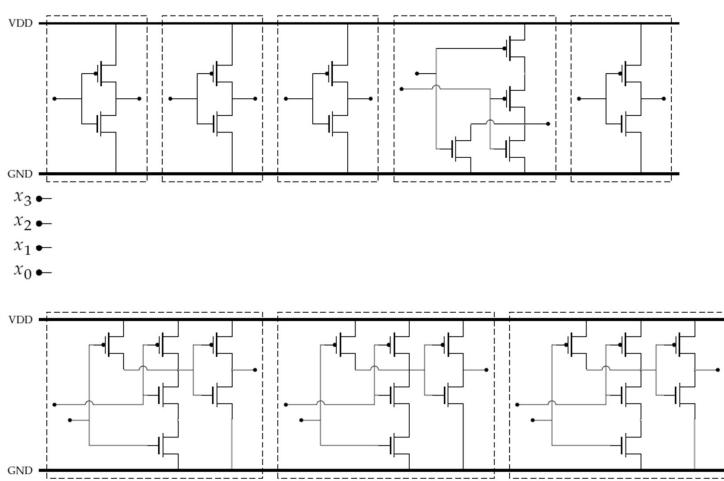

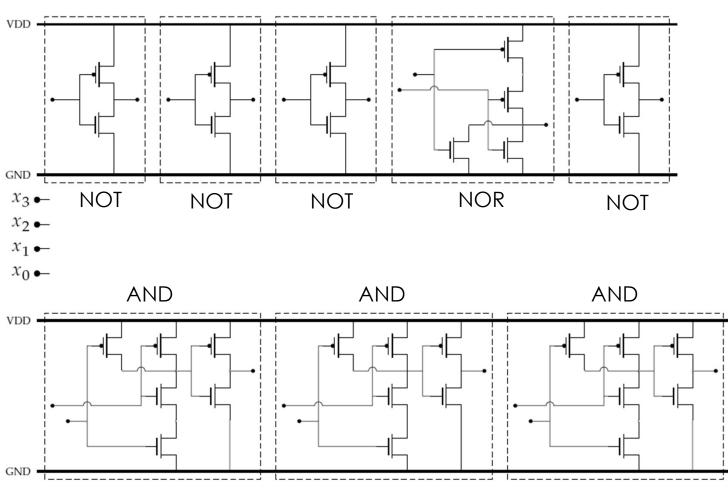

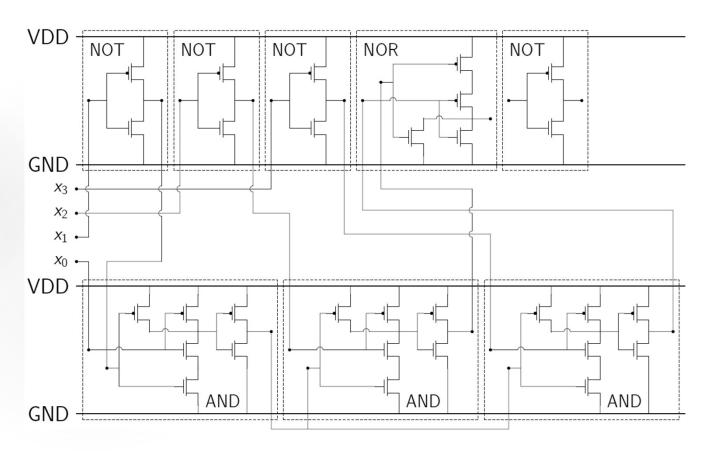

- ► Standardzellen sind vorgefertigte CMOS-Realisierungen einfacher Schaltfunktionen, wie zum Beispiel Und, Oder oder Nicht, die im Baukastenprinzip zusammengesetzt werden können.

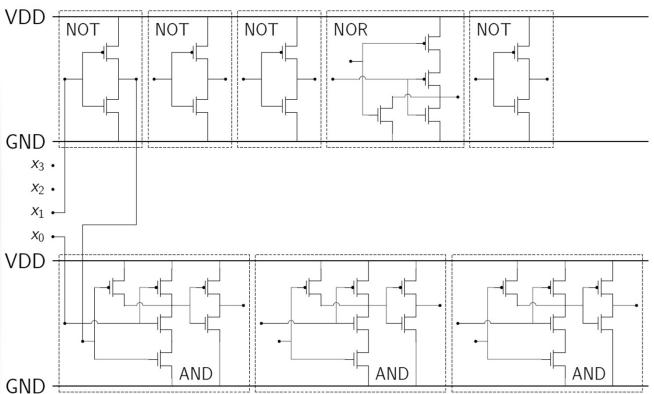

- ► Schalten Sie die folgenden Standardzellen so zusammen, dass sie *f* realisieren

Hinweis: die einzelnen Standardzellen sind gestrichelt umrahmt.

# Aufgabe 1 – CMOS

### Aufgabe 1 – CMOS

► Gehen wir die einzelnen Gatter durch

Pull-Up:  $\bar{x}$

Pull-Down:  $x \rightarrow Negation: \bar{x}$

Hatte ich ja schon einmal als Beispiel:

Der Inverter!

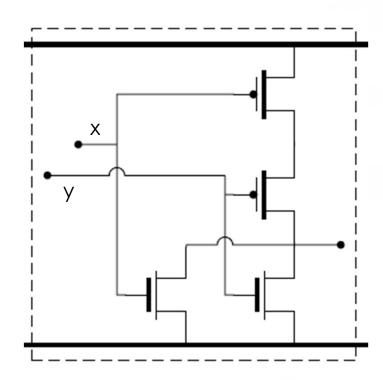

### Aufgabe 1 – CMOS

► Gehen wir die einzelnen Gatter durch

Pull-Up:  $\bar{x} \cdot \bar{y} = \overline{x+y}$

Pull-Down: x + y

$\rightarrow$  *Negation*:  $\overline{x+y}$

Das NOR-Gatter.

### Aufgabe 1 – CMOS

Gehen wir die einzelnen Gatter durch

Pull-Up:  $\overline{x} + \overline{y} = x \cdot y$

Pull-Down:  $\overline{x \cdot y}$

$\rightarrow$  *Negation*:  $\overline{\overline{x \cdot y}} = x \cdot y$

NAND-Gatter links wird invertiert!

Das AND-Gatter.

#### Hinweis:

Das Schaltnetz kann auf Grund des Verknüpfungspunkts (o), an dem Pull-Up und Pull-Down zusammengeführt werden, in zwei Bereiche aufgeteilt werden.

Diese kann man am besten separat voneinander auswerten!

▶ Umformen des Ausdrucks, so dass unsere Gatter ausreichen

Wir haben: 4 NOT, 1 NOR, 3 ANDs

$$f(x_3,x_2,x_1,x_0) = x_0 \,\overline{x_1} \,\overline{x_2} + x_0 \,\overline{x_1} \,\overline{x_3} \qquad | \text{ kein ODER (Doppelnegation)}$$

$$= \overline{(x_0 \,\overline{x_1} \,\overline{x_2}) + (x_0 \,\overline{x_1} \,\overline{x_3})} \qquad | \text{ großes NOR unter Negation}$$

$$= \overline{(A \,\overline{x_2}) + (A \,\overline{x_3})} \qquad | \text{ Wiederverwenden von A} = x_0 \,\overline{x_1}$$

Geht genau auf © Was für ein Zufall ...

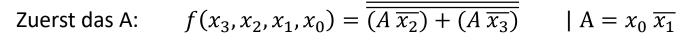

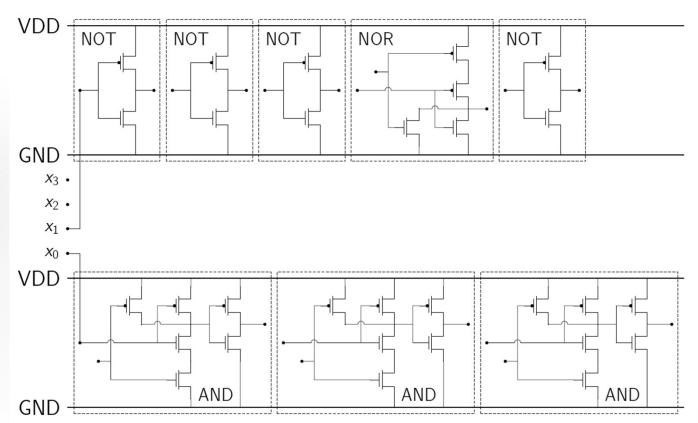

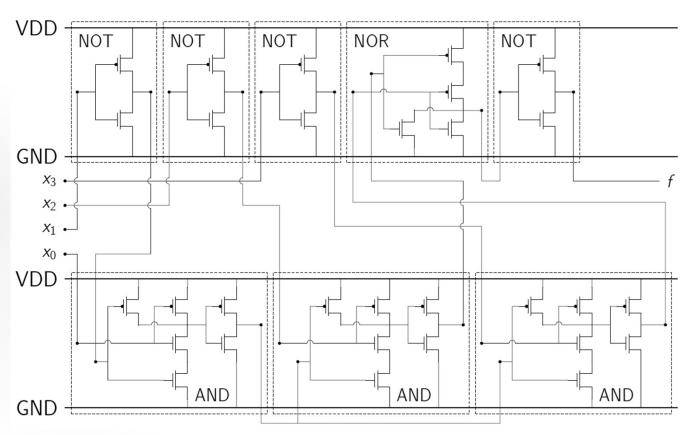

### Aufgabe 1 – CMOS

# Aufgabe 1 – CMOS

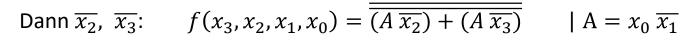

Zuerst das A:  $f(x_3, x_2, x_1, x_0) = \overline{(A \overline{x_2}) + (A \overline{x_3})}$   $| A = x_0 \overline{x_1} |$

### Aufgabe 1 – CMOS

### Aufgabe 1 – CMOS

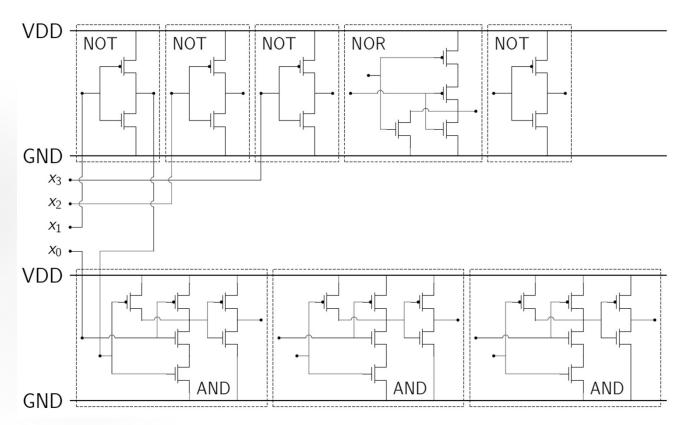

Dann die ANDs:

$$f(x_3, x_2, x_1, x_0) = \overline{\overline{(A \overline{x_2}) + (A \overline{x_3})}} \qquad | A = x_0 \overline{x_1}$$

$$\mid A = x_0 \overline{x_1}$$

### Aufgabe 1 – CMOS

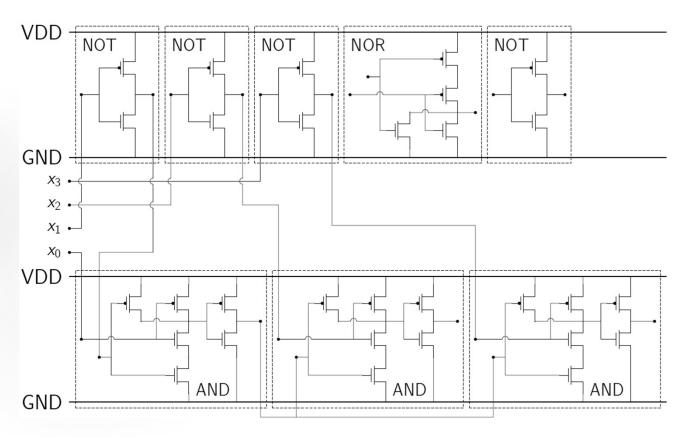

Dann das NOR:

$$f(x_3, x_2, x_1, x_0) = \overline{(\overline{A} \overline{x_2}) + (\overline{A} \overline{x_3})} \qquad | A = x_0 \overline{x_1}$$

$$| A = x_0 \overline{x_1}$$

Dann negieren. Fertig:

$$f(x_3, x_2, x_1, x_0) = \overline{\overline{(A \overline{x_2}) + (A \overline{x_3})}} \qquad | A = x_0 \overline{x_1}$$

$$\mid A = x_0 \overline{x_1}$$

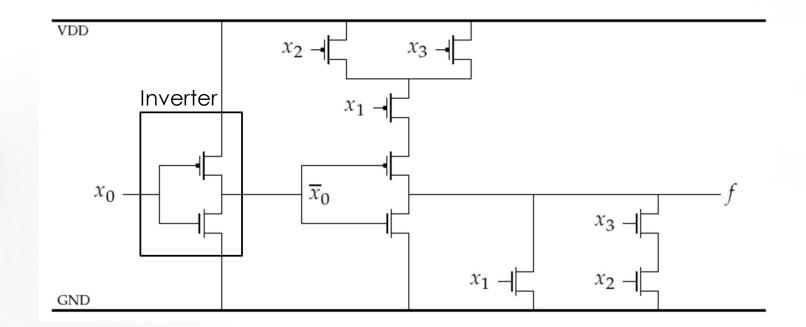

► Realisieren Sie die Schaltfunktion f (x3, x2, x1, x0) als CMOS-Schaltung mit möglichst wenig Transistoren, wobei alle Eingänge nur in der nicht invertierten Form zur Verfügung stehen.

CMOS-Schaltung mit möglichst wenig Transistoren, wobei alle Eingänge nur in der nicht invertierten Form zur Verfügung stehen.

Minimieren des Ausdrucks:

$$f(x_3, x_2, x_1, x_0) = x_0 \overline{x_1} \overline{x_2} + x_0 \overline{x_1} \overline{x_3}$$

| Distributivgesetz

=  $x_0 \overline{x_1} (\overline{x_2} + \overline{x_3})$

PMOS-Ausdruck (alle Literale sind negiert):

$$f_{PMOS} = x_0 \overline{x_1} (\overline{x_2} + \overline{x_3})$$

(x<sub>0</sub> wird durch einen Inverter negiert)

NMOS-Ausdruck (alle Literale sind nicht negiert):

$$f_{\text{NMOS}} = \overline{f_{\text{PMOS}}} = \overline{x_0} \, \overline{x_1} (\, \overline{x_2} + \overline{x_3})$$

| De Morgan  $= \overline{x_0} + x_1 + x_2 x_3$

$$f_{PMOS} = x_0 \, \overline{x_1} (\, \overline{x_2} + \overline{x_3})$$

$$f_{PMOS} = x_0 \overline{x_1} (\overline{x_2} + \overline{x_3})$$

$f_{NMOS} = \overline{x_0} + x_1 + x_2 x_3$

► Vergleichen Sie die Anzahl benötigter Transistoren in a) und b). Für welche Anwendungsfälle eignen sich die beiden Entwurfsmethoden jeweils?

Hinweis: Gates zählen

▶ Vor und Nachteile von a) und b) und Anwendungsfälle

#### Gatteranzahl:

- a) 30 Transistoren

- b) 10 Transistoren

Sieger b): Implementierung ist schneller und platzsparender (auf Chip).

### Automatisierbarkeit:

a) Sehr einfach

b) Schwer und komplizierter

Sieger a): Billigere Produktionskosten, da nur automatische "Verkabelung" nötig. Massenproduktion von Basiselementtafeln möglich.

### ► Beschreibung:

Mit Hilfe von NAND-Gattern, kann jede beliebige Schaltfunktion realisiert werden (Gleiches gilt für die Verwendung von NOR-Gattern.). Realisieren Sie nun die Schaltfunktion:

$$f = AC\overline{D} + \overline{A}\overline{C} + BC + B\overline{D}$$

Unter ausschließlicher Verwendung von NAND-Gattern, die zwei Eingänge besitzen. Wie viele NAND-Gatter sind erforderlich?

Basissysteme:

Ein Basissystem ist erzeugend (und minimal?), d.h. jede beliebige Schaltfunktion kann durch alleinigen Einsatz der Komponenten des Basissystems realisiert werden.

Korollar: Jedes Basissystem kann in jedes andere Basissystem umgeformt werden.

### Bedeutende Basissysteme:

- NAND

- NOR

- AND, OR, Negation (Es reicht auch: AND, Negation bzw. OR, Negation)

### ► Basissysteme:

| Zahl der<br>Operatoren | Namen      | Zeichen        | Darstellung<br>mit UND,<br>ODER,NICHT                  | a′               | Darstellung von a' a&b a+b                                          |                                                                     |  |

|------------------------|------------|----------------|--------------------------------------------------------|------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|--|

|                        | NICHT      |                |                                                        |                  | 100                                                                 | a · 0                                                               |  |

| 3                      | NICHT      | y= a'          | -                                                      | a′               | -                                                                   | -                                                                   |  |

|                        | UND        | y=a&b          |                                                        | -                | y=a&b                                                               | -                                                                   |  |

|                        | ODER       | y=a+b          |                                                        | -                | -                                                                   | y=a+b                                                               |  |

| 2                      | NICHT      | y= a'          | -                                                      | a′               | -                                                                   | $a \lor b = \overline{a \lor b}$                                    |  |

|                        | UND        | y=a&b          |                                                        | -                | y=a&b                                                               | $=\overline{\overline{a}\wedge\overline{b}}$                        |  |

| 2                      | NICHT      | y= a'          | -                                                      | a′               | $a \wedge b = \overline{a \wedge b}$                                | -                                                                   |  |

|                        | ODER       | y=a+b          |                                                        | -                | $=\overline{\overline{a}\vee\overline{b}}$                          | y=a+b                                                               |  |

| 2                      | UND        | y=a&b          | y=a&b                                                  | a <b>≠</b> 1     | y=a&b                                                               |                                                                     |  |

|                        | Antivalenz | y=a <b>±</b> b | $y = \overline{a} \wedge b \vee a \wedge \overline{b}$ |                  | -                                                                   | $a \oplus b \oplus (a \wedge b)$                                    |  |

| 1                      | NAND       | y=a&b          | $y = a \wedge b$                                       | a&a              | $\overline{a \wedge b} =$                                           | $\overline{a} \wedge \overline{b} =$                                |  |

|                        |            |                | $=\overline{a}\vee\overline{b}$                        | 1&a              | $(a \overline{\wedge} b) \overline{\wedge} (a \overline{\wedge} b)$ | $(a \overline{\wedge} a) \overline{\wedge} (b \overline{\wedge} b)$ |  |

| 1                      | NOR        | y=a+b          | $y = \overline{a \lor b}$                              | a+a              | $\overline{\overline{a} \vee \overline{b}} = \overline{a \vee b} =$ | $\overline{a \lor b} = \overline{a \lor b} =$                       |  |

|                        |            |                | $=\overline{a}\wedge\overline{b}$                      | 0 <del>-</del> a | $(a \overline{\lor} a) \overline{\lor} (b \overline{\lor} b)$       | $(a \lor b) \lor (a \lor b)$                                        |  |

► Nandisierung/Norisierung:

Um einen beliebigen aussagenlogischen Ausdruck in eine Nand-Form oder Nor-Form mit zwei Eingängen zu bringen wenden wir folgende Gesetze an:

Doppelnegation, De Morgan, 1 bzw. 0 Erweiterung

NAND:

$$A \to \bar{\bar{A}} \to \; \overline{\overline{A1}1}$$

$$A \to \bar{\bar{A}} \to \overline{\overline{A+0}+0}$$

$$AB \rightarrow \overline{\overline{AB}} \rightarrow \overline{\overline{AB}} 1$$

$$AB \rightarrow \overline{\overline{AB}} \rightarrow \overline{\overline{A} + \overline{B}} \rightarrow \overline{\overline{A} + 0} + \overline{B} + \overline{0}$$

$$A + B \rightarrow \overline{\overline{A + B}} \rightarrow \overline{A}\overline{B} \rightarrow \overline{\overline{A1}}\overline{B1}$$

$A + B \rightarrow \overline{\overline{A + B}} \rightarrow \overline{\overline{A + B}} + \overline{0}$

$$A + B \rightarrow \overline{\overline{A + B}} \rightarrow \overline{\overline{A + B}} + 0$$

Wir können so jeden Ausdruck analog schrittweise umformen.

► Nandisierung/Norisierung:

Falls kein 1 oder 0 Eingang zur Verfügung steht, verdoppelt man einfach den Eingang und hat somit aus einem, zwei Eingänge gemacht!

NAND:

$$A \to \overline{\overline{A}} \to \overline{\overline{A11}} \to \overline{\overline{AA}} \overline{\overline{AA}}$$

$$AB \to \overline{\overline{AB}} \to \overline{\overline{AB}} \to \overline{\overline{AB}} \overline{\overline{AB}}$$

$$A \rightarrow \overline{A} \rightarrow \overline{A+0} + 0 \rightarrow \overline{A+A} + \overline{A+A}$$

$$AB \rightarrow \overline{\overline{AB}} \rightarrow \overline{\overline{A} + \overline{B}} \rightarrow \overline{\overline{A} + \overline{A} + \overline{B} + \overline{B}}$$

Sowas kommt manchmal in der Miniklausur vor ...

... erhöht den Schreibaufwand aber nochmal deutlich.

$$f = AC\overline{D} + \overline{A}\overline{C} + BC + B\overline{D}$$

Das Vorgehen: erst gesamt doppelt negieren und dann schrittweise auf die kleineren Terme zurückführen bis alles durch NAND mit zwei Eingängen substituiert ist

$$f = \overline{\overline{AC\overline{D}} + \overline{A}\overline{C} + BC + B\overline{D}}$$

| Doppelnegation (Gesamt)

$$= \overline{\overline{AC\overline{D}} \cdot \overline{A}\overline{C} \cdot \overline{BC} \cdot \overline{B}\overline{D}}$$

| De Morgan

$$= \overline{\overline{AC\overline{D1}} \cdot \overline{A1} \overline{C1} \cdot \overline{BC} \cdot \overline{B}\overline{D1}}$$

| Erweitern mit 1

Wir wollen überall genau zwei Eingänge haben. Um mehrere Eingänge eines NAND auf zwei Eingänge zu reduzieren, doppelnegieren wir partiell und nutzen die Erweiterung mit 1.

$$f = AC\overline{D} + \overline{A}\overline{C} + BC + B\overline{D}$$

$$f = \overline{\overline{AC}\overline{D1}} \cdot \overline{\overline{A1}} \overline{C1} \cdot \overline{BC} \cdot \overline{B}\overline{D1}$$

$$= \overline{\overline{\overline{AC}}} \overline{\overline{D1}} \cdot \overline{\overline{A1}} \overline{C1} \cdot \overline{BC} \cdot \overline{B}\overline{D1}$$

$$= \overline{\overline{\overline{AC}}} \overline{\overline{D1}} \cdot \overline{\overline{A1}} \overline{C1} \cdot \overline{BC} \cdot \overline{BD1}$$

$$= \overline{\overline{\overline{AC}}} \overline{\overline{D1}} \cdot \overline{\overline{A1}} \overline{C1} \cdot \overline{BC} \cdot \overline{BD1}$$

| 1 Erweiterung

Den gleichen Trick nutzt man für den Gesamtterm. Man zergliedert diesen in zwei Hälften und jene ggf. dann wiederum in zwei Hälften, bis wir bei genau einem oder zwei verknüpften Teiltermen angekommen sind.

$$= \overline{\overline{\overline{AC1}} \overline{D1} \cdot \overline{\overline{A1}} \overline{C1}} 1 \cdot \overline{1} \overline{\overline{BC}} \cdot \overline{\overline{BD1}}$$

Man benötigt insgesamt also 15 NAND-Gatter mit zwei Eingängen.

Man sieht: Diese Aufgabe macht immer besonders viel Spaß ☺

Anmerkung, um diese schöne Aufgabe zu rechtfertigen:

"Bei einer Implementierung von Logikfunktionen in CMOS-Technologie stehen dem Designer oft nur NAND-Gatterzellen mit fester Anzahl der Eingänge zur Verfügung (meistens nur zwei). Die Gründe dafür sind vor allem eine sehr starke Verschlechterung der Gatterlaufzeit in Abhängigkeit von der Anzahl (sog. fan in) und der aktuellen Belegung der Eingänge, die im schlimmsten Fall sogar quadratisch mit der Anzahl der Eingänge ansteigt. Zusätzlich erhöht sich auch der Energieverbrauch bei einer größeren Anzahl der Eingänge beträchtlich (mehr Transistoren, in CMOS immer 2\*Anzahl der Eingänge, verbrauchen mehr Energie)."

Na ja <sup>©</sup> Warum man das per Hand machen muss ...

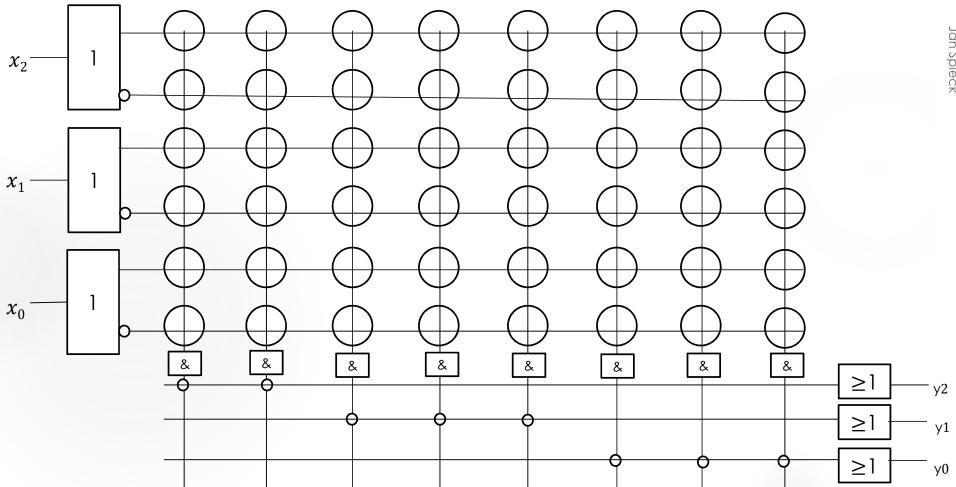

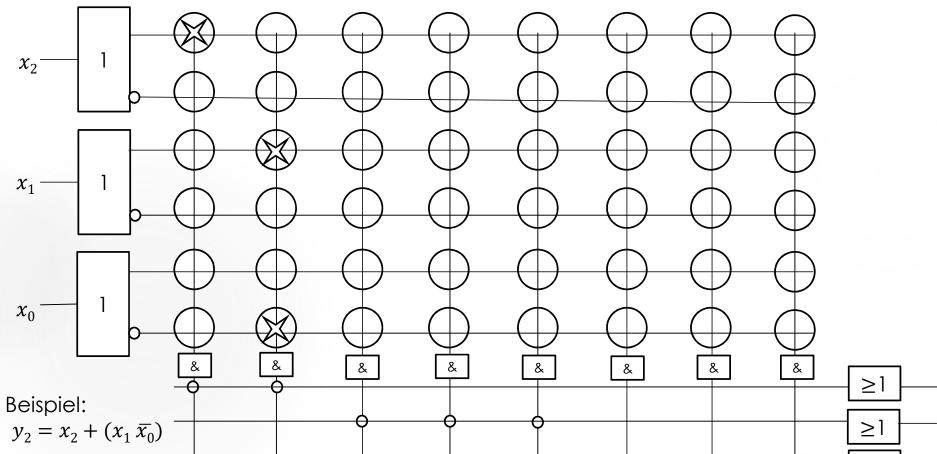

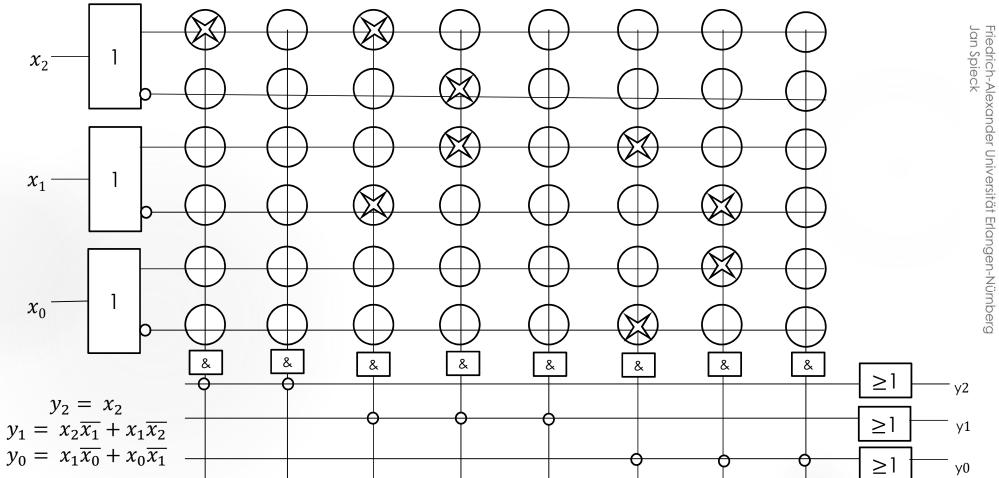

### Aufgabe 3 – PAL

▶ Beschreibung:

Realisieren Sie einen Codeumsetzer, der eine 3 Bit Binärzahl in einen zyklischen Graycode umwandelt. Verwenden Sie dazu die gegebene PAL (Programmable Array Logic) Struktur.

Friedrich-Alexander Universität Erlangen-Nürnberg Jan Spieck

▶ Begriffsklärung

#### PAL:

- Programmable Array Logic, d.h. es können konjunktive Terme über ein Feld frei programmiert werden

- Schaltung zur Repräsentation einer DMF

- Erste Stufe: Auswahl der Literale für konjunktive Terme (Verundung der

- selektierten Literale) (programmierbar)

- Zweite Stufe: Auswahl der programmierten konjunktiven Terme (fest)

#### Weitere wichtige Schaltungstypen im Vergleich:

- PAL (Programmable Array Logic):

- o Programmierbare UND-Matrix, feste ODER-Matrix

- PLA (Programmable Logic Array):

- o Programmierbare UND-Matrix, programmierbare ODER-Matrix

- ULA (Universal Logic Array):

- Feste UND-Matrix, feste ODER-Matrix

- o Auswahl der 2<sup>n</sup> Minterme programmierbar

- ROM (Read Only Memory):

- Feste UND-Matrix, programmierbare ODER-Matrix

$\geq$

Friedrich-Alexander Universität Erlangen-Nürnberg Jan Spieck

y0

# Friedrich-Alexander Universität Erlangen-Nürnberg Jan Spieck

# Aufgabe 3 – PAL

Codeumsetzer: 3 Bit Binärzahl -> zyklischer Graycode

#### Darstellung der Schaltfunktion in einer Tabelle:

| X <sub>2</sub> | <b>x</b> <sub>1</sub> | X <sub>0</sub> | <b>y</b> <sub>2</sub> | <b>y</b> <sub>1</sub> | <b>y</b> <sub>0</sub> |

|----------------|-----------------------|----------------|-----------------------|-----------------------|-----------------------|

| 0              | 0                     | 0              | 0                     | 0                     | 0                     |

| 0              | 0                     | 1              | 0                     | 0                     | 1                     |

| 0              | 1                     | 0              | 0                     | 1                     | 1                     |

| 0              | 1                     | 1              | 0                     | 1                     | 0                     |

| 1              | 0                     | 0              | 1                     | 1                     | 0                     |

| 1              | 0                     | 1              | 1                     | 1                     | 1                     |

| 1              | 1                     | 0              | 1                     | 0                     | 1                     |

| 1              | 1                     | 1              | 1                     | 0                     | 0                     |

Auslesen der Schaltfunktionen (alternativ Schaltfunktionen im Symmetriediagramm)

$$y_{2} = x_{2}$$

$$y_{1} = x_{2}\overline{x_{1}} + x_{1}\overline{x_{2}}$$

$$y_{0} = x_{1}\overline{x_{0}} + x_{0}\overline{x_{1}}$$

| X <sub>2</sub> | <b>x</b> <sub>1</sub> | X <sub>0</sub> | <b>y</b> <sub>2</sub> | <b>y</b> <sub>1</sub> | <b>y</b> <sub>0</sub> |

|----------------|-----------------------|----------------|-----------------------|-----------------------|-----------------------|

| 0              | 0                     | 0              | 0                     | 0                     | 0                     |

| 0              | 0                     | 1              | 0                     | 0                     | 1                     |

| 0              | 1                     | 0              | 0                     | 1                     | 1                     |

| 0              | 1                     | 1              | 0                     | 1                     | 0                     |

| 1              | 0                     | 0              | 1                     | 1                     | 0                     |

| 1              | 0                     | 1              | 1                     | 1                     | 1                     |

| 1              | 1                     | 0              | 1                     | 0                     | 1                     |

| 1              | 1                     | 1              | 1                     | 0                     | 0                     |

#### Denkpause

Aufgabe: Scherzfragen

1: Wo kommt Silvester vor Weihnachten?

2: Was sagt der Weihnachtsmann, wenn er kopfüber in den Kamin fällt?

3: Es hängt an der Dachrinne und muss weinen, wenn die Sonne wird wieder scheinen.

Vier Wichtel A, B, C und D, werden eines Tages vom Weihnachtsmann beim Stehlen erwischt, bekommen eine Kappe aufgesetzt und werden in den Schnee eingegraben. Zwischen C und D befindet sich ein Felsen. Beide können also keinen der anderen sehen. B kann nur C sehen. A kann B und C sehen. Keiner kann jedoch seinen eigenen Hut sehen.

Der Weihnachtsmann verkündet: "Kann einer von ihnen seine eigene Kappenfarbe nennen, so kommen alle frei. Schafft es keiner oder rät einer falsch, benutze ich euch als Golfbälle."

Die Wichtel wissen, dass es genau zwei rote und zwei violette Kappen gibt. Nach fünf Minuten löst einer das Rätsel und sagt seine eigene Kappenfarbe. Wer und wie hat er es gemacht?

#### Denkpause

#### Lösung:

1: Im Wörterbuch

2: Oh Oh Oh

3: Eiszapfen

Wichtel B sagt seine Kappenfarbe.

Er hat wohl folgenden Gedankengang gehabt: "Wenn mein Kappe so wie die meines Vordermannes C violett wäre, dann hätte A sofort gewusst, dass sein eigener Hut rot sein muss. Da A aber schon seit fünf Minuten schweigt muss mein Hut rot sein, denn nur dann kann A nicht wissen, welche Farbe sein Hut hat."

# Latches und Flipflops Endlich mal speichern

#### Beschreibung

In dieser Aufgabe sollen die Eigenschaften ausgesuchter Flipflopschaltungen untersucht werden. Die Verzögerungszeit eines jeden Logikgatters beträgt hierbei  $\tau=1~\mathrm{ns}$

#### Begriffsklärung

#### Speicherelement:

- o Gerät/Modul, das einen zuvor angelegten Wert unbegrenzt speichert

- Charakteristische Tabelle:

| Befehl                    | Q(t): aktueller Zustand | Q(t+1): nächster Zustand |

|---------------------------|-------------------------|--------------------------|

| Set (S)                   | -                       | 1                        |

| Reset (R)                 | -                       | 0                        |

| Speichern/ keine Änderung | 0                       | 0                        |

|                           | 1                       | 1                        |

#### Aktivierungsmechanismen:

- Pegelsteuerung

- Pegel auf High (aktiviert)

- Pegel auf Low (deaktiviert)

- Flankensteuerung

- Positive/steigende Flanke (aktiviert)

- Negative/fallende Flanke (aktiviert)

#### Änderungszeitpunkte:

Synchron: zu festen durch den Takt (Clock) vorgegebenen Zeitpunkte

(1) während des Pegels oder (2) während einer Flanke

o Asynchron: zu beliebigen Zeitpunkten

#### Flipflop:

- Speicherelement zur Speicherung eines Bits

- Verschiedene Arten der Umsetzung (RS, JK, Master-Slave, D, ...)

- Zwei konträre gängige Definitionen:

- Rein flankengesteuerte Speicherelemente

- o Überbegriff für jegliche Speicherelemente

#### Latch:

- Pegelgesteuertes Flipflop

- Deutsche Bezeichnung: transparentes Flipflop

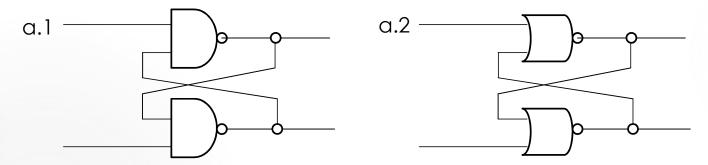

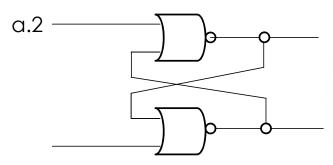

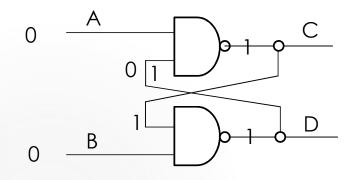

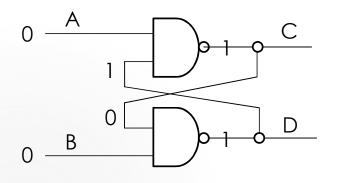

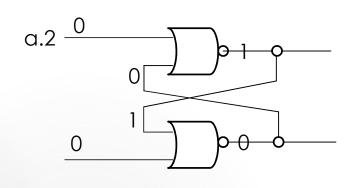

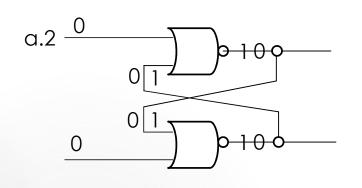

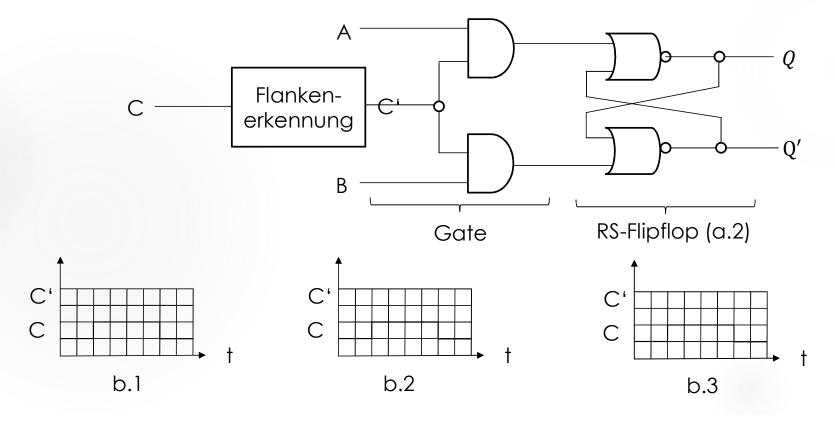

► An die Eingänge (A, B) der Schaltungen (a.1) und (a.2) werden nacheinander die Werte aus der Tabelle angelegt. Vervollständigen Sie die Tabelle und geben Sie den Signalen A bis D jeweils sinnvolle Bezeichnungen.

| Α | В | C1 | D1 | C2 | D2 |

|---|---|----|----|----|----|

| 0 | 1 |    |    |    |    |

| 0 | 0 |    |    |    |    |

| 1 | 1 |    |    |    |    |

| 1 | 0 |    |    |    |    |

| 1 | 1 |    |    |    |    |

| 0 | 0 |    |    |    |    |

Wir betrachten die Schalttabellen von NAND und NOR-Gattern

NOR:

Ausgang 0, sobald mind. eine 1

NAND:

Ausgang 1, sobald mind. eine 0

| Α | В | NOR | NAND |

|---|---|-----|------|

| 0 | 0 | 1   | 1    |

| 0 | 1 | 0   | 1    |

| 1 | 0 | 0   | 1    |

| 1 | 1 | 0   | 0    |

Dies gilt es zu beachten, da die Rückkoppelung bei diesen Fällen keine Änderung mehr hervorruft – wir also in einem stabilen Zustand landen (solange A und B konstant).

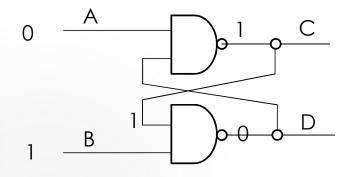

▶ Beginnen wir mit dem Flipflop a.1. Um die Einträge der Tabelle zu bekommen, legen wir an die Eingänge A und B jeweils die geforderten Werte (0 bzw. 1) an und geben den stabilen Endzustand an (falls dieser existiert)

| Α | В | С | D |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 0 | 0 |   |   |

| 1 | 1 |   |   |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

| 0 | 0 |   |   |

- 1: Eine 0 am Eingang eines NAND impliziert eine 1 am Ausgang.

- 2: Zwei Einsen am Eingang eines NAND implizieren eine 0 am Ausgang Dadurch ändert sich der Wert von C nicht (stabiler Endzustand)

► Ebenso verfahren wir für die anderen Kombinationen an den Eingängen A und B und beachten dabei die vorherige Belegung

| Α | В | С | D |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 1 |

| 1 | 1 |   |   |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

| 0 | 0 |   |   |

- 1: Durch die vorherige Belegung liegen 0 und 1 an je einem NAND-Eingang

- 2: Durch die Nullen am zweiten Eingang ergeben sich an den Ausgängen zwei Einsen Die neue 1 am oberen NAND-Eingang ändert nichts am Ausgang (stabiler Zustand).

Dieser Zustand ist unzulässig; dies werden wir bei späteren FFs vermeiden.

► Ebenso verfahren wir für die anderen Kombinationen an den Eingängen A und B und beachten dabei die vorherige Belegung

| Α | В | С | D |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 1 |

| 1 | 1 | Ś | Ś |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

| 0 | 0 |   |   |

- 1: Durch die vorherige Belegung liegt jeweils eine 1 an einem NAND-Eingang

- 2: Somit ergeben sich am Ausgang zwei Nullen

- 3: Diese Nullen implizieren am Ausgang wieder zwei Einsen. Gehe zu Schritt 2.

Wir bekommen also eine Oszillation zwischen 0 und 1 am Ausgang (instabil!)

► Ebenso verfahren wir für die anderen Kombinationen an den Eingängen A und B und beachten dabei die vorherige Belegung

| Α | В | С | D |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 1 |

| 1 | 1 | Ś | Ś |

| 1 | 0 | 0 | 1 |

| 1 | 1 |   |   |

| 0 | 0 |   |   |

- 1: Die untere 0 impliziert eine 1 am Ausgang

- 2: Jene 1 impliziert am oberen NAND eine 0 am Ausgang

Dieser Zustand ist stabil, da sich durch die neue 0 nichts mehr ändert.

► Ebenso verfahren wir für die anderen Kombinationen an den Eingängen A und B und beachten dabei die vorherige Belegung

| Α | В | С | D |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 1 |

| 1 | 1 | Ś | Ś |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 |

| 0 | 0 |   |   |

- 1: Aus der vorherigen Belegung resultierte eine 0 und eine 1

- 2: Somit ändert sich am Ausgang nichts mehr -> keine Änderung

► Ebenso verfahren wir für die anderen Kombinationen an den Eingängen A und B und beachten dabei die vorherige Belegung

| Α | В | С | D  |

|---|---|---|----|

| 0 | 1 | 1 | 0  |

| 0 | 0 | 1 | 1  |

| 1 | 1 | Ś | ç. |

| 1 | 0 | 0 | 1  |

| 1 | 1 | 0 | 1  |

| 0 | 0 | 1 | 1  |

- 1: Aus der vorherigen Belegung resultierte eine 0 und eine 1

- 2: Beide Nullen implizieren eine 1 am Ausgang.

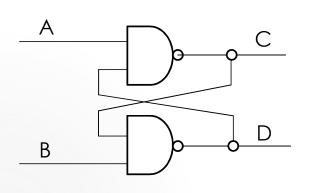

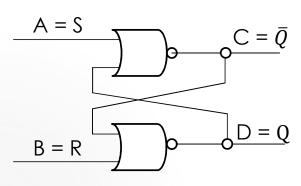

▶ Betrachten wir nun die Tabelle zur Benennung der Ein- und Ausgänge

| Α | В | С | D | Entspricht     |

|---|---|---|---|----------------|

| 0 | 1 | 1 | 0 | Reset/Set      |

| 0 | 0 | 1 | 1 | Ungültig!      |

| 1 | 1 | ś | Ś | Oszillation    |

| 1 | 0 | 0 | 1 | Set/Reset      |

| 1 | 1 | 0 | 1 | Keine Änderung |

| 0 | 0 | 1 | 1 | Ungültig!      |

| Befehl         | Q(t): aktueller Zustand | Q(t+1): nächster Zustand |

|----------------|-------------------------|--------------------------|

| Set (S)        | -                       | 1                        |

| Reset (R)      | -                       | 0                        |

| Speichern/     | 0                       | 0                        |

| keine Änderung | 1                       | 1                        |

Betrachten wir nun die Tabelle zur Benennung der Ein- und Ausgänge

| Α | В | С | D | Entspricht     |

|---|---|---|---|----------------|

| 0 | 1 | 1 | 0 | Reset/Set      |

| 0 | 0 | 1 | 1 | Ungültig!      |

| 1 | 1 | ś | Ś | Oszillation    |

| 1 | 0 | 0 | 1 | Set/Reset      |

| 1 | 1 | 0 | 1 | Keine Änderung |

| 0 | 0 | 1 | 1 | Ungültig!      |

Wir haben ein asynchrones Flipflop (keine Clock) mit einem ungültigen Zustand. Dies ist also eine R/S-Flipflop. Laut Definition erreicht man einen ungültigen Zustand durch das Eingangstupel (1,1) und nicht (0,0), weshalb wir unsere Eingänge als negiert annehmen. Wir definieren uns A als negierten Reset-Eingang und B als negierten Set-Eingang (auch andersherum möglich). Damit ist  $C = \overline{Q}$  und D = Q.

Diese Art von Flipflop nennt man Active-low. (da negierter Eingang)

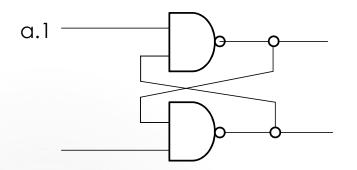

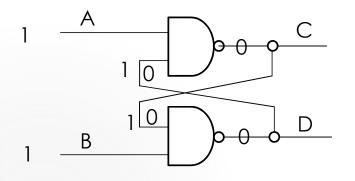

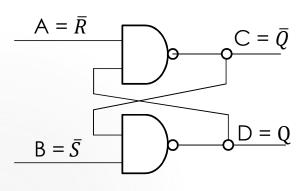

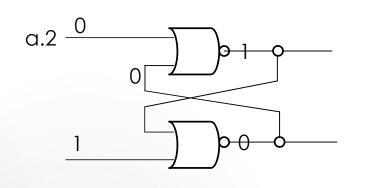

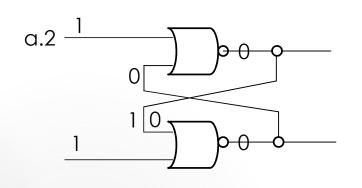

► Nun betrachten wir den zweiten Flipflop a.2:

| Α | В | С | D |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 0 | 0 |   |   |

| 1 | 1 |   |   |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

| 0 | 0 |   |   |

- 1: Aus der unteren 1 resultiert eine 0 am Ausgang

- 2: Beide Nullen implizieren eine 1 am oberen Ausgang.

► Nun betrachten wir den zweiten Flipflop a.2:

| Α | В | С | D |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 0 |

| 1 | 1 |   |   |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

| 0 | 0 |   |   |

- 1: Aus der vorherigen Belegung ergibt sich eine alte 0 und 1

- 2: Durch die angelegten Nullen ändert sich nichts an der Ausgabe

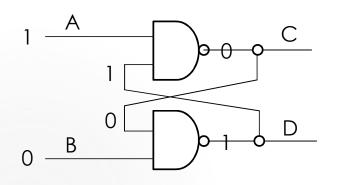

► Nun betrachten wir den zweiten Flipflop a.2:

| Α | В | С | D |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

| 0 | 0 |   |   |

- 1: Aus der vorherigen Belegung ergibt sich eine alte 0 und 1

- 2: Durch die angelegten Einsen ergeben sich oben und unten zwei Nullen

- 3: Die neue 0 am unteren NOR verändert die Ausgabe nicht

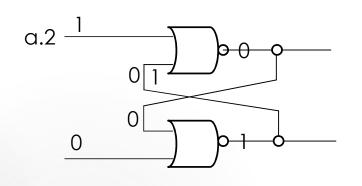

► Nun betrachten wir den zweiten Flipflop a.2:

| A | В | С | D |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 |   |   |

| 0 | 0 |   |   |

- 1: Aus der vorherigen Belegung ergibt sich zwei alte Nullen

- 2: Am unteren NOR ergibt sich am Ausgang so eine 1

- 3: Die neue 1 am oberen NOR verändert die Ausgabe nicht

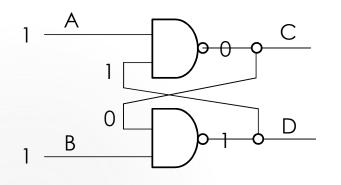

► Nun betrachten wir den zweiten Flipflop a.2:

| Α | В | С | D |  |

|---|---|---|---|--|

| 0 | 1 | 1 | 0 |  |

| 0 | 0 | 1 | 0 |  |

| 1 | 1 | 0 | 0 |  |

| 1 | 0 | 0 | 1 |  |

| 1 | 1 | 0 | 0 |  |

| 0 | 0 |   |   |  |

- 1: Aus der vorherigen Belegung ergibt sich eine alte 1 und eine 0

- 2: Die beiden neuen Einsen ergeben am Ausgang zwei Nullen

- 3: Die neue 0 am oberen NOR verändert die Ausgabe nicht

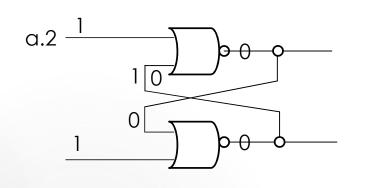

► Nun betrachten wir den zweiten Flipflop a.2:

| Α | В | С | D |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 |

| 0 | 0 | Ś | Ś |

- 1: Aus der vorherigen Belegung ergeben sich zwei alte Nullen

- 2: Somit ergibt sich oben wie unten eine 1 am Ausgang

- 3: Die neuen Einsen ergeben wiederum Nullen am Ausgang (Wdh. Schritt 2)

Dieser Zustand ist instabil! Es kommt zur Oszillation

▶ Betrachten wir nun die Tabelle zur Benennung der Ein- und Ausgänge

| Α | В | С | D | Entspricht     |

|---|---|---|---|----------------|

| 0 | 1 | 1 | 0 | Reset/Set      |

| 0 | 0 | 1 | 0 | Keine Änderung |

| 1 | 1 | 0 | 0 | Ungültig!      |

| 1 | 0 | 0 | 1 | Set/Reset      |

| 1 | 1 | 0 | 0 | Ungültig!      |

| 0 | 0 | ś | Ś | Oszillation    |

Wir haben ein asynchrones Flipflop (keine Clock) mit einem ungültigen Zustand. Dies ist also eine R/S-Flipflop. Laut Definition erreicht man einen ungültigen Zustand durch das Eingangstupel (1,1), weshalb wir unsere Eingänge als nicht negiert annehmen. Wir definieren uns A als Set-Eingang und B als Reset-Eingang (auch andersherum möglich). Damit ist  $C = \bar{Q}$  und D = Q

Diese Art von Flipflop nennt man Active-high. (da nicht-negierter Eingang)

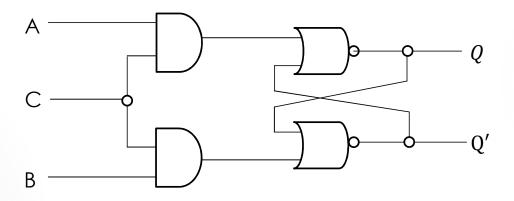

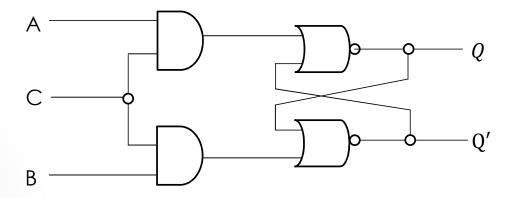

► Wie bezeichnet man folgendes Flipflop?

Hinweis: C steht für Clock

Wie bezeichnet man folgendes Flipflop?

Solange C = 0 ist das Gate deaktiviert, da an den Ausgängen immer (0,0) anliegt.

Bei C = 1, kann man sich das UND-Gatter wegdenken und es werden A und B weitergeleitet (aktiviert). Das Flipflop ist also ein pegelgesteuertes RS-Flipflop.

Außerdem ist es wieder Active-high.

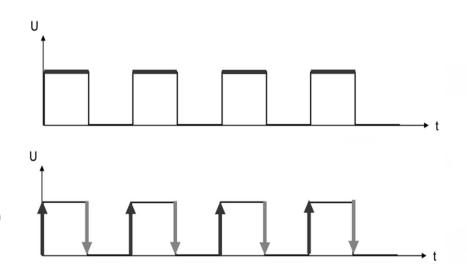

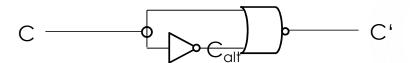

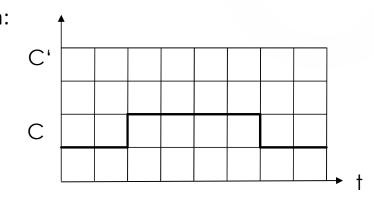

▶ Das Flipflop soll so erweitert werden, dass es bei der steigenden (b.1), der fallenden (b.2) und bei jeder Flanke (b.3) die Daten übernimmt. Geben Sie jeweils das Schaltnetz und das zugehörige Zeitverhalten der Flankenerkennung an.

Verzögerungsstrategien

Es gibt verschiedene Verzögerungsarten, um ein C<sub>alt</sub> zu bekommen.

- Inverter:

- o geringe Verzögerung

- Man erhält ein negiertes C<sub>alt</sub>

- o UND/ODER:

- o mittlere Verzögerung

- Man erhält ein nicht neg. C<sub>alt</sub>

- Sonstige Gatter:

- NAND/NOR genutzt, da geringere Verzögerung als AND/ODER (Latenz)

- Andere Gatter werden auch hin und wieder verwendet

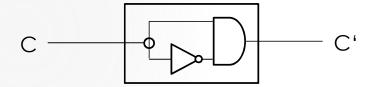

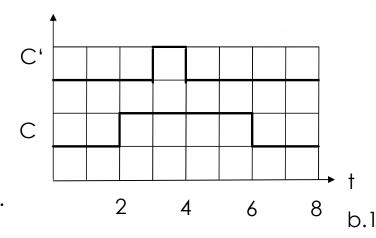

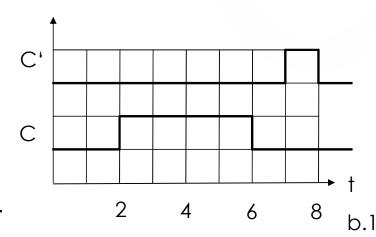

▶ Das Flipflop soll so erweitert werden, dass es bei der steigenden Flanke die Daten übernimmt. Geben Sie jeweils das Schaltnetz und das zugehörige Zeitverhalten der Flankenerkennung an.

Wir wissen, dass die Verzögerungszeit  $\tau = 1$  beträgt.

Wir wollen folgendes Verhalten (pro t = 1) umsetzen:

| Calt | C <sub>neu</sub> | C'           |  |

|------|------------------|--------------|--|

| 0    | 0                | 0            |  |

| 0    | 1                | 1 (steigend) |  |

| 1    | 0                | 0 (fallend)  |  |

| 1    | 1                | 0            |  |

b.1

$$f(C_{alt}, C_{neu}) = \overline{C_{alt}} \cdot C_{neu}$$

▶ Das Flipflop soll so erweitert werden, dass es bei der steigenden Flanke die Daten übernimmt. Geben Sie jeweils das Schaltnetz und das zugehörige Zeitverhalten der Flankenerkennung an.

Wir wissen, dass die Verzögerungszeit  $\tau=1$  beträgt. Dadurch entsteht ein  $C_{\rm alt}$  nach dem Inverter, da die obere Leitung keine Verzögerung besitzt.

$$f(C_{alt}, C_{neu}) = \overline{C_{alt}} \cdot C_{neu}$$

Das UND-Gatter verzögert das C' um eine Zeiteinheit.

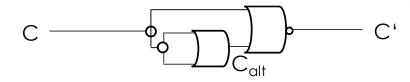

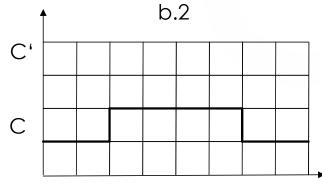

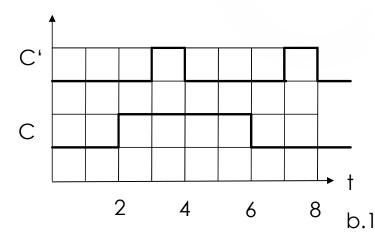

▶ Das Flipflop soll so erweitert werden, dass es bei der fallenden Flanke die Daten übernimmt. Geben Sie jeweils das Schaltnetz und das zugehörige Zeitverhalten der Flankenerkennung an.

Wir wissen, dass die Verzögerungszeit  $\tau=1$  beträgt. Wir wollen folgendes Verhalten (pro t=1) umsetzen:

| Calt | C <sub>neu</sub> | C'           |

|------|------------------|--------------|

| 0    | 0                | 0            |

| 0    | 1                | 0 (steigend) |

| 1    | 0                | 1 (fallend)  |

| 1    | 1                | 0            |

Problem: Wir bekommen durch einen Inverter nur  $\overline{C_{alt}}$ , deshalb formen wir um  $f(C_{alt}, C_{neu}) = \overline{C_{neu}} \cdot C_{alt} = \overline{\overline{C_{alt}}} + C_{neu}$

▶ Das Flipflop soll so erweitert werden, dass es bei der steigenden Flanke die Daten übernimmt. Geben Sie jeweils das Schaltnetz und das zugehörige Zeitverhalten der Flankenerkennung an.

Wir wissen, dass die Verzögerungszeit  $\tau=1$  beträgt. Dadurch entsteht ein  $C_{alt}$  nach dem Inverter, da die obere Leitung keine Verzögerung besitzt. Wir nutzen ein NOR.

$$f(C_{alt}, C_{neu}) = \overline{\overline{C_{alt}} + C_{neu}}$$

Das NOR-Gatter verzögert das C' um eine Zeiteinheit.

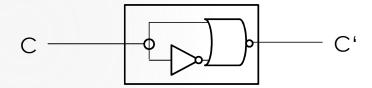

▶ Das Flipflop soll so erweitert werden, dass es bei beiden Flanken die Daten übernimmt. Geben Sie jeweils das Schaltnetz und das zugehörige Zeitverhalten der Flankenerkennung an.

Wir wissen, dass die Verzögerungszeit  $\tau=1$  beträgt. Wir wollen folgendes Verhalten (pro t=1) umsetzen:

| Calt | C <sub>neu</sub> | C,           |

|------|------------------|--------------|

| 0    | 0                | 0            |

| 0    | 1                | 1 (steigend) |

| 1    | 0                | 1 (fallend)  |

| 1    | 1                | 0            |

$$f(C_{alt}, C_{neu}) = \overline{C_{neu}} \cdot C_{alt} + \overline{C_{alt}} \cdot C_{neu} = (\overline{C_{neu}} + \overline{C_{alt}}) \cdot (C_{alt} + C_{neu})$$

$$= \overline{\overline{C_{alt}}} \, \overline{C_{neu}} + C_{alt} \, C_{neu} = \overline{\overline{C_{alt}}} \oplus C_{neu}$$

▶ Das Flipflop soll so erweitert werden, dass es bei der steigenden Flanke die Daten übernimmt. Geben Sie jeweils das Schaltnetz und das zugehörige Zeitverhalten der Flankenerkennung an.

Wir wissen, dass die Verzögerungszeit  $\tau=1$  beträgt. Dadurch entsteht ein  $C_{alt}$  nach dem Inverter, da die obere Leitung keine Verzögerung besitzt. Wir nutzen ein XNOR.

$$f(C_{alt}, C_{neu}) = \overline{C_{alt}} \oplus C_{neu}$$

Das XNOR-Gatter verzögert das C' um eine Zeiteinheit.

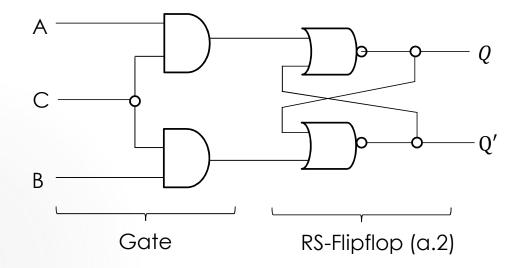

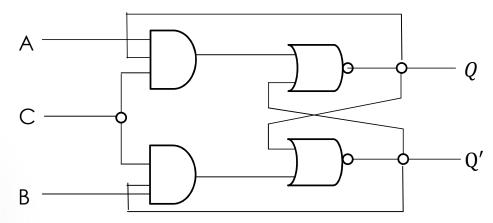

► Erweitern Sie nun die Schaltung dahingehend, dass keine undefinierten Zustände, wie sie in Aufgabe a) der Fall waren, mehr auftreten.

Hinweis: der ungültige Zustand trat bei A = 1 und B = 1 auf. Wir bauen uns jetzt ein JK-Flipflop

# Friedrich-Alexander Universität Erlangen-Nürnberg Jan Spieck

#### Aufgabe 4 – Flipflops

Lösung: Rückleiten der Ausgabe Q/Q' in die Flankensteuerung

Der ungültige Zustand trat bei A = 1 und B = 1 auf.

Wir sperren nun einen der Eingänge A und B, wenn Q bzw. Q' vorher 0 ist. Dadurch haben wir eine Differenzierung zwischen oben und unten.

Wir umgehen somit gleiche Werte.

| Α | В | С | D | Entspricht     |

|---|---|---|---|----------------|

| 0 | 1 | 1 | 0 | Reset/Set      |

| 0 | 0 | 1 | 0 | Keine Änderung |

| 1 | 1 | 0 | 0 | Ungültig!      |

| 1 | 0 | 0 | 1 | Set/Reset      |

| 1 | 1 | 0 | 0 | Ungültig       |

| 0 | 0 | Ś | Ś | Oszillation    |

#### Vielen Dank für eure großzügige Aufmerksamkeit

'Ci sono soltanto due possibili conclusioni: se il risultato conferma le ipotesi, allora hai appena fatto una misura; se il risultato è contrario alle ipotesi, allora hai fatto una scoperta.'

Enrico Fermi

Dizionario Biografico degli Italiani, vol. 46.